4G multi-mode encoderProduct code: TC1750 |

|

|

|

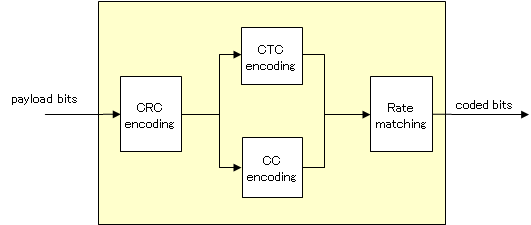

TC1750 is a high throughput turbo/convolutional code encoder covering LTE, HSPA+, WiMAX 16e/m. It performs either convolutional turbo code (CTC) encoding or convolutional code (CC) encoding and rate matching for these three PHY layer specifications.

The rate matching is flexible and can easily be used to execute HARQ mechanism. Thanks to its high throughput architeture TC1750 is able to reach multi-Gbits/s throughput ranges with a single core instance:

- up to 4 Gbits/s payload rate in LTE mode (with 500 MHz clock)

- up to 1 Gbits/s payload rate in HSPA mode (with 500 MHz clock)

Functional coverage:

The core is not a simple turbo encoder accelerator, but offers the support of rate matching functions (see below) that off-loads the DSP from this tasks without requiring an additional hardware module.

- 3GPP LTE mode

- CRC encoding

- CTC block sizes range: 40 to 6144 bits

- CC block sizes: 8 to 1024 bits

- rate matching: bit collection, sub-block interleaving, bit selection

- 3GPP-HSPA+ mode

- CTC block sizes range: 40 to 5114 bits

- CC block sizes range: 8 to 504 bits

- rate-matching: bit separation, puncturing / repetition, bit collection

- IEEE802.16d/e/m WiMAX mode

- CRC encoding

- CTC block sizes: 48 to 4800 bits

- CC block sizes: 48 to 288 bits

- rate matching: sub-block interleaving, bit grouping, bit selection

Features:

- Block-by-block change of physical layer mode (LTE/HSPA+/WiMAX), block length, rate matching parameters

- Latency reduction by bank swapping

- No external memory required

- High throughput architecture

- Silicon proven

- ASIC Core: Verilog or VHDL RTL source code

- FPGA Core available on all popular Altera, Lattice and Xilinx devices

Related Cores:

- 5G LDPC encoder/decoder

- 5G Polar encoder/decoder

- 4G multi mode decoder (TC1700)

- LTE / Wifi Viterbi decoder (TC1720)

- HSPA encoder Core covering CTC encoding + rate-matching (TC7100enc)

- LTE encoder Core covering CC and CTC encoding + sub-block interleaver (TC7000enc_LTE)

- WiMAX encoder Core covering CC and CTC encoding + sub-block interleaver (TC1000enc_WiMAX)