4G multi-mode turbo decoderProduct code: TC1700 |

|

|

|

TC1700 is a turbo decoder adressing LTE, LTE-A, WiMAX, HSPA/+, and legacy 3G standard.

The core uses a unique architecture that reduces by more than 50 % the silicon area when compared to separate single-mode Cores, with no restrictions on the flexibility and features set. The core can also be tailored efficiently to single mode core as LTE only for example.

Thanks to its unique flexible pipe-line architecture, the core can be configured into 2 performance profiles:- high performance profile for Base Station receiver

- low power profile for User Equipement receiver

- 1X throughput level: 12.5 to 25 Mbits/s @ 8 it., depending on selected profile and target process.

- 8X throughput level: 150 to 300 Mbits/s @ 8 it., depending on selected profile and target process.

- 16X throughput level: 300 to 600 Mbits/s @ 8 it. and up to 1 Gbits/s @ 5 it., depending on selected profile and target process.

The core is based on our robust and silicon-proven architecture that has been adopted by leading 4G system-on-chip manufacturers for both BS and UE receivers.

Its unique architecture is optimized for ASIC targets, but can be targeted efficiently for FPGA as well.

Functional coverage:

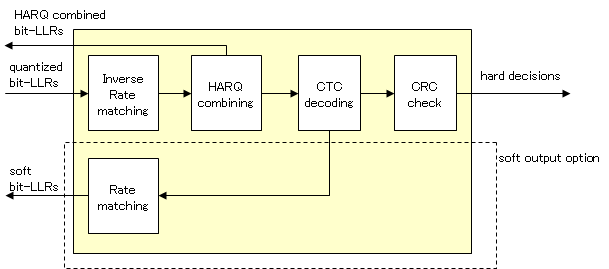

The core offers much more than a turbo decoding functionality: it covers the support of LTE and HSPA rate matching functions (see below) that off-loads the DSP from this tasks without requiring an additional hardware module.

- 3GPP LTE mode

- block sizes range: 40 to 6144 bits

- rate matching: insertion of NULL bits, sub-block deinterleaving, bit collection

- CRC decoding

- HARQ combining (including inverse bit-selection)

- 3GPP-HSPA+ mode

- block sizes range: 40 to 5114 bits

- rate-matching for E-DCH and HS-DSCH transport channels: inverse puncturing and repetition, inverse bit-selection

- HARQ combining for E-DCH transport channel (including inverse bit-collection)

- IEEE802.16d/e/m WiMAX mode

- maximum block size: 60 or 600 bytes (selectable)

- depuncturing, sub-block deinterleaving

- CRC check in 16m mode

The core can optionally provide soft outputs for all the coded bits (including rate matching of samples), which can be used for advanced iterative receivers.

Features:

- Near ideal error decoding performance

- Block-by-block change of physical layer mode (HSPA+/LTE/WiMAX), block length, and number of iterations

- Very efficient early stopping algorithm for reducing average number of iterations (reduced power consumption, higher average throughput)

- Latency reduction by bank swapping

- No external memory required

- Channel BER estimator

- Selectable quantization level - prior synthesis (4 to 8 bits LLR quantization)

- Bypassable rate matching functions

- Low power architecture

- Silicon proven (several UE and BS tapeouts)

- ASIC Core: Verilog or VHDL RTL source code

- FPGA Core available on all popular Altera, Lattice and Xilinx devices

Related Cores:

Other products / services are available. Contact us for more details.- 5G LDPC encoder/decoder

- 5G Polar encoder/decoder

- Multi mode CTC / CC encoder (TC1750)

- LTE / Wifi Viterbi decoder (TC1720)

- LTE Cat-0 CTC decoder (TC1770)

- LTE CTC decoder (TC7000-LTE)

- Multiple instante LTE CTC decoder (TC1714)

- HSPA encoder Core covering CTC encoding + rate-matching (TC7100enc)

- LTE encoder Core covering CC and CTC encoding + sub-block interleaver (TC7000enc_LTE)

- WiMAX encoder Core covering CC and CTC encoding + sub-block interleaver (TC1000enc_WiMAX)