LTE turbo decoderProduct code: TC7000 LTE |

|

TC7000-LTE is a convolutional turbo code (CTC) decoder optimized for FPGAs. Its unique pipe-line architecture enables to reach very high clock frequencies on high end FPGAs. It offers several algorithm options to meet various trade-offs between error correction performance versus Core complexity.

The decoder architecture is very flexible and offers several levels of throughput for different complexity throughput requirements. Throughput depends on the selected device and vary with the block size and number of iterations. Typical figures with 4 decoding iterations are given below for high end FPGAs.

- 1-processors Core: 40 Mbits/s

- 2-processors Core: 70 Mbits/s

- 4-processors Core: 140 Mbits/s

- 8-processors Core: 250 Mbits/s

Functional coverage:

- block sizes range: 40 to 6144 bits

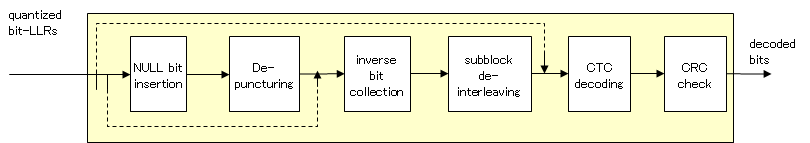

- rate matching: insertion of NULL bits, sub-block deinterleaving, bit collection

- CRC decoding

Features:

- Near floating point error correction performance

- High throughput Max-Log-MAP algorithm

- Efficient and flexible optional Log-MAP algorithm

- Multi-processor architecture, several throughput levels selectable before synthesis - from 75 to 300 Mbits/s decoded

- Optimal iteration stopping feature for reducing average number of iterations without performance degradation

- On-the-fly change of block length and number of iterations

- Low latency

- No external memory required

- Available on all popular Xilinx, Altera and Lattice devices

- FPGA proven

Related Cores:

- 4G multi mode decoder (TC1700)

- Multi mode CTC / CC encoder (TC1750)

- Multi mode Viterbi decoder (TC2000)

- LTE encoder Core covering CC and CTC encoding + sub-block interleaver (TC7000enc_LTE)